Ziel dieses Projektes

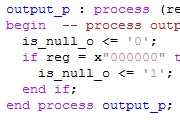

Ziel dieses Projektes war es einen ADS-B Decoder in VHDL zu entwerfen der den Datenstrom aus einem 1090MHz Empfänger möglichst effizient auswertet. Herausgekommen ist ein leistungsstarker FPGA basierter Decoder. Die digitale Schaltung wurde in VHDL geschrieben. Durch verschiedene Verarbeitungsstufen und den Verzicht auf externe Module wie Prozessoren arbeitet der Dekoder sehr schnell und zuverlässig. Die Daten werden anschließen über eine RS232-Schnittstelle an einen PC übertragen. Durch verschiedene Maßnahmen (z.B. Datenpufferung für die serielle Datenübertragung und CRC Korrektur) konnten die Verluste durch die langsame übertragungsgeschwindigkeit einer seriellen Schnittstelle weitestgehend kompensiert werden. Das Projekt wurde von den Studenten Carsten Fischbeck und Frank Kuhlmann im Rahmen ihres Elektrotechnikstudiums, Vertiefung technische Informatik, durchgeführt.